集成电路版图设计是现代芯片制造的基石,而Cadence作为该领域的行业标准工具,其掌握程度直接关系到设计工程师的效率和成果质量。本文旨在为读者提供一个从理论到实践、从入门到精通的综合性指南,涵盖版图设计核心概念与Cadence软件工具的有效运用。

一、集成电路版图设计基础

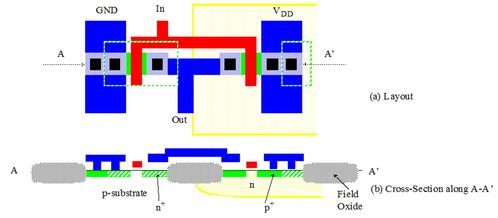

版图设计是将电路原理图转化为一系列可供光刻使用的几何图形(几何层)的过程。这不仅仅是简单的图形绘制,更是一门融合了电学、物理学和制造工艺的精密艺术。核心要点包括:

- 设计规则检查(DRC):确保版图符合芯片代工厂的工艺制造约束,如最小线宽、最小间距等,避免制造失败。

- 电路图与版图一致性检查(LVS):验证绘制出的物理版图与原始电路原理图在电气连接和元件特性上完全一致。

- 寄生参数提取与后仿真:提取版图中由连线等引入的寄生电阻、电容,并进行仿真,以确保电路性能在物理实现后仍能满足指标。

- 可靠性考量:如天线效应、闩锁效应(Latch-up)、电迁移(EM)等的预防与设计。

扎实理解这些基础,是高效使用任何EDA工具(包括Cadence)的前提。

二、Cadence软件平台概览与核心工具

Cadence提供了一整套完整的IC设计平台。对于版图设计工程师而言,核心工具主要包括:

- Virtuoso Layout Suite:这是进行实际版图编辑和物理验证的旗舰环境。它提供了强大的图形编辑功能、层次化设计管理以及与其他验证工具的无缝集成。

- Virtuoso Schematic Editor:用于绘制和编辑电路原理图,是版图设计的起点。

- Assura / PVS:Cadence的物理验证工具,用于执行DRC、LVS、寄生参数提取(RCX)等关键检查。

- Allegro:在更大规模的封装和PCB设计领域也广泛应用,与芯片版图设计协同工作。

掌握这些工具的组合使用,是完成一个完整设计流程的关键。

三、版图设计流程与Cadence实践

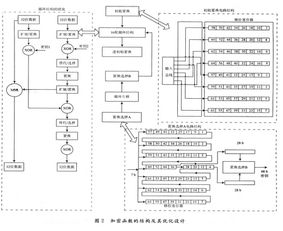

一个典型的基于Cadence的版图设计流程如下:

- 前期准备与规划:在Virtuoso中建立设计库、工艺文件(PDK)关联。根据电路模块和性能要求,规划版图的整体布局、电源地线分布、信号流走向。

- 单元版图绘制:使用Virtuoso Layout Editor,从最底层的晶体管、电阻、电容等开始绘制。熟练运用图形创建、复制、对齐、属性编辑等功能,并严格遵守DRC规则。

- 层次化设计与集成:将绘制好的基本单元进行组合,构建更复杂的子模块和顶层模块。合理利用层次化可以极大提高设计复用性和管理效率。

- 物理验证:

- 使用Assura运行DRC,根据错误报告逐项修改版图。

- 运行LVS,解决任何原理图与版图不匹配的问题。

- 运行寄生参数提取,生成带寄生信息的网表。

- 后仿真与优化:将提取的寄生网表导入仿真环境(如Spectre),进行后仿真。根据性能下降情况,返回版图进行迭代优化(如调整布线、屏蔽敏感信号等)。

- 最终验证与交付:完成所有验证后,生成最终用于流片的GDSII文件。

四、软件开发技能在版图设计中的赋能作用

现代版图设计已远非纯手动操作。掌握一定的软件开发技能能显著提升工作效率和设计质量:

- Skill语言:Cadence Virtuoso内置的基于Lisp的编程语言。可用于编写自定义的版图生成脚本、自动完成重复性任务、创建复杂的PCELL(参数化单元)、开发定制化菜单和工具。这是高级版图工程师的核心技能之一。

- Ocean脚本:用于自动化仿真和后处理分析,可以批量运行仿真、提取数据并生成报告。

- Python/Tcl/Perl:用于编写流程自动化脚本,管理设计数据,集成不同EDA工具,以及进行文本处理和数据分析。

- 用户自定义函数(UDF):在验证工具中编写规则检查的补充代码。

通过编程,可以将设计经验固化为自动化流程,减少人为错误,并处理手工无法完成的复杂结构设计。

五、学习路径与资源建议

对于初学者或希望系统提升的工程师:

- 夯实基础:首先理解半导体器件原理和CMOS工艺基础。

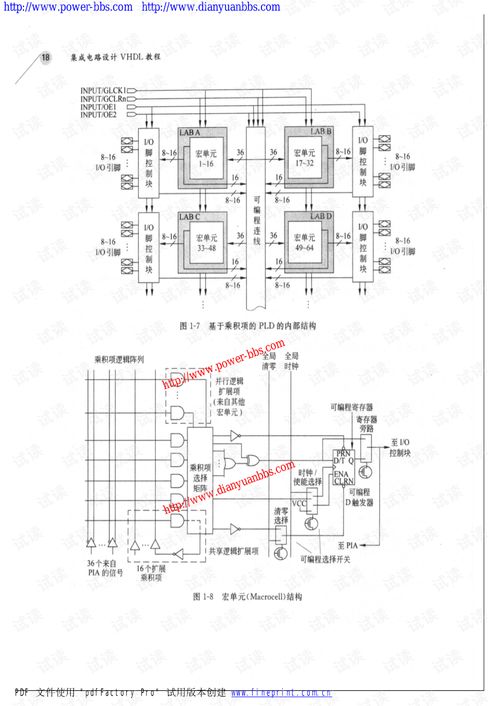

- 工具入门:通过Cadence官方文档、培训课程或如“eetop.cn”等专业论坛上的入门教程(例如《集成电路版图layout设计与cadence讲义》这类资料),熟悉Virtuoso等图形界面的基本操作。

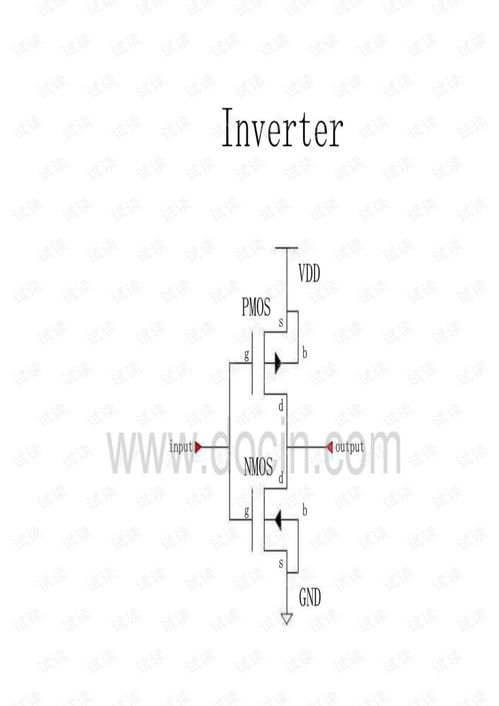

- 项目实践:从简单的反相器、与非门等标准单元入手,完成从原理图到GDSII的完整流程,深刻理解DRC/LVS。

- 进阶提升:学习Skill或Python编程,尝试自动化简单任务,并研究更复杂的模拟电路版图(如运放、PLL)或数字电路模块的布局布线技巧。

- 持续学习:关注工艺演进、EDA工具更新,并积极参与技术社区讨论。

###

集成电路版图设计是连接电路创意与物理芯片的桥梁。精通Cadence等EDA工具,并辅以必要的软件开发能力,将使设计工程师如虎添翼,能够应对日益复杂的芯片设计挑战,在确保功能正确和性能优异的不断提升设计效率,最终成功交付可制造的芯片版图。这条学习之路需要耐心与实践,但其回报是与现代信息技术核心共成长的满足感与职业竞争力。