超大规模集成电路(VLSI)的设计是一个极其复杂且高度系统化的工程过程,其核心目标是将数百万乃至数十亿个晶体管及互连线,按照特定的功能与性能要求,精准地集成到一块微小的硅片上。本部分将深入探讨集成电路设计的基本流程、主要设计方法以及各个设计阶段的关键任务。

一、集成电路设计的基本流程

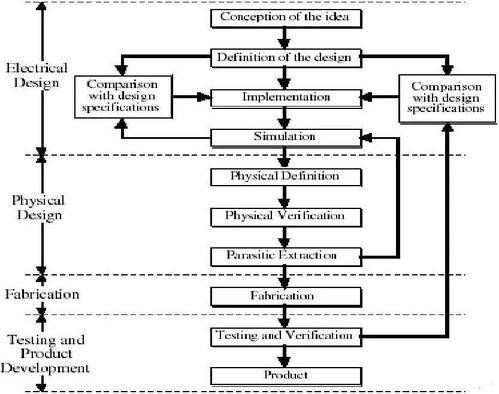

集成电路设计通常遵循一个分层化、模块化的设计流程,主要可以划分为以下几个关键阶段:

- 系统规划与行为级描述:这是设计的起点。设计者根据芯片需要完成的功能(如数据处理、信号传输等),进行系统级的架构划分和性能指标定义。通常使用高级硬件描述语言(如SystemVerilog、SystemC)或数学建模工具对系统的整体行为进行抽象描述和仿真验证。

- 逻辑设计:将行为级描述转换为由基本逻辑门(如与门、或门、非门、触发器等)构成的网表。这一阶段的核心任务是逻辑综合,即利用综合工具,在满足时序、面积、功耗等约束条件下,将寄存器传输级(RTL)代码自动优化并映射到目标工艺库的标准逻辑单元上,生成门级网表。

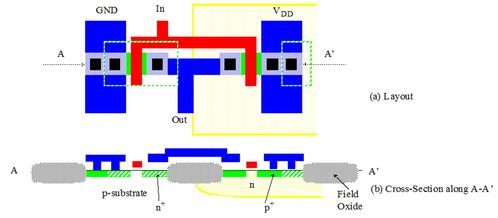

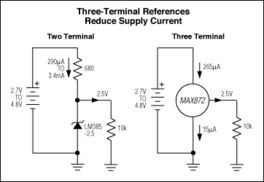

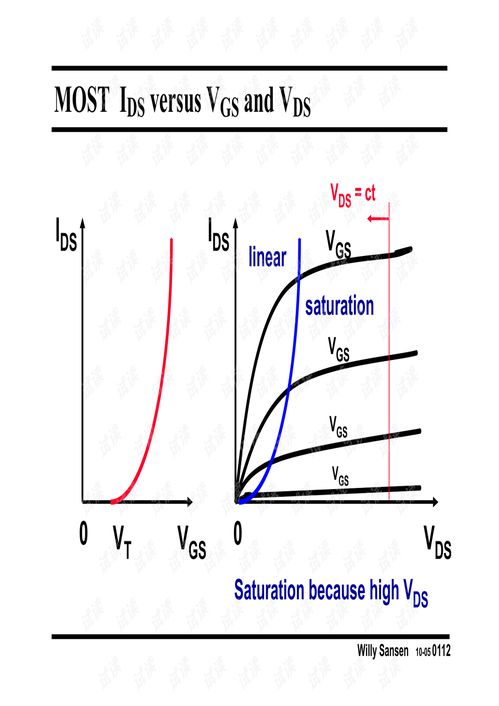

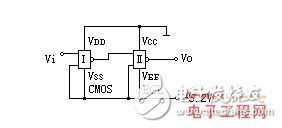

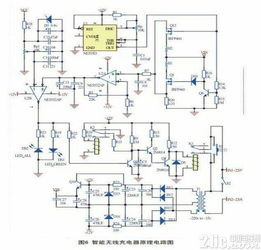

- 电路设计:将门级网表进一步细化到晶体管级。设计者需要确定每个逻辑门的晶体管尺寸、连接方式以及驱动能力,确保电路在速度、功耗和噪声容限之间取得平衡。对于高性能或模拟电路模块,此阶段往往需要手工精心设计。

- 物理设计:这是将电路网表转化为实际几何版图(Layout)的过程,是连接设计与制造的桥梁。主要包括:

- 布图规划与布局:确定芯片上各个功能模块(如CPU核、内存、接口)的大致位置和形状,以及所有标准单元的摆放位置,目标是优化布线资源、缩短关键路径延时。

- 时钟树综合:构建一个低偏斜、低功耗的全局时钟分布网络,确保时钟信号能够几乎同步地到达所有时序单元。

- 布线:根据电路的电气连接关系,在遵守设计规则的前提下,完成所有单元之间金属连线的物理路径规划。

- 物理验证:对生成的版图进行设计规则检查(DRC)、电气规则检查(ERC)和版图与电路图一致性检查(LVS),确保其符合代工厂的工艺要求和设计的电气功能。

- 验证与签核:贯穿于整个设计流程。除了各阶段的功能仿真,在物理设计完成后,还需要进行包含实际寄生参数(电阻、电容)的后仿真,以及静态时序分析(STA)、电源完整性分析、信号完整性分析等,以确保芯片在真实物理条件下能够正确、可靠地工作,最终达到可以交付制造的“签核”标准。

二、主要设计方法

面对VLSI的复杂性,工程师主要采用两种互补的设计方法:

- 自顶向下设计:这是主流的设计范式。从最高抽象级别的系统规格开始,逐层进行功能分解和细化,直至底层的物理实现。每一层都进行建模、仿真和验证,确保下层实现符合上层的功能定义。这种方法有利于管理复杂性,提高设计重用性,并支持团队并行开发。

- 自底向上设计:基于已有的、经过验证的底层单元(如标准逻辑单元、存储器编译器生成的模块、IP核等)来构建更复杂的系统。在基于标准单元库和IP复用的现代设计中,物理设计阶段很大程度上是自底向上的。通常,自顶向下和自底向上的方法会在设计流程中结合使用。

三、现代设计的关键支撑技术

- 电子设计自动化工具:EDA工具链是VLSI设计的生命线,涵盖了从仿真、综合、布局布线到验证的所有环节,极大地提升了设计效率和可靠性。

- 知识产权核复用:广泛使用经过预设计、预验证的IP核(如处理器核、接口控制器、存储器等),是快速构建复杂SoC芯片的基石。

- 可制造性设计:在设计中预先考虑制造工艺的波动和限制,通过添加冗余结构、优化图形等方式,提高芯片的良率和可靠性。

超大规模集成电路设计是一个融合了系统架构、微电子学、计算机科学和精密工程的综合性学科。其严谨的分层设计流程与先进的EDA方法学,共同构成了将创新思想转化为硅片上现实功能的坚实桥梁。理解这一完整的设计脉络,是深入VLSI领域的基础。