在信息技术飞速发展的今天,集成电路(Integrated Circuit, IC)作为现代电子系统的核心基石,其设计与制造水平直接决定了计算能力、通信效率和智能设备的发展边界。其中,超大规模集成电路(Very Large Scale Integration, VLSI)设计,作为集成电路领域的高阶形态,承载着将数以亿计甚至百亿计的晶体管集成到单一芯片上的重任,是驱动从个人电脑、智能手机到数据中心、人工智能和物联网等所有前沿科技持续创新的关键引擎。

一、VLSI设计:从概念到硅片的核心流程

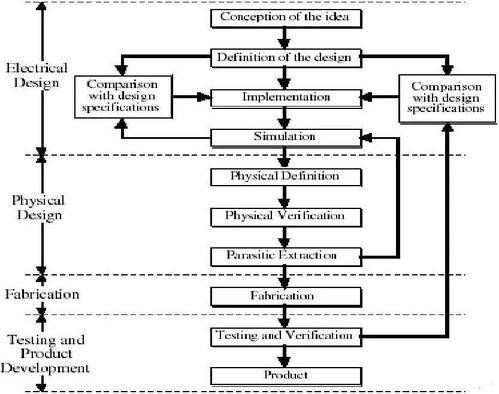

超大规模集成电路设计是一个极度复杂、多学科交叉的系统工程,其核心目标是在满足性能、功耗、面积和成本等多重约束下,将抽象的电路功能或系统架构转化为可在硅片上制造的物理版图。这一过程通常遵循一个层次化、迭代的设计流程:

- 系统架构与功能定义:根据芯片的应用场景(如CPU、GPU、AI加速器),确定其顶层功能、性能指标和外部接口。

- 寄存器传输级设计:使用硬件描述语言(如Verilog或VHDL)将系统功能转化为寄存器级的逻辑描述,这是设计过程中关键的“软”模型阶段。

- 逻辑综合与验证:通过电子设计自动化工具,将RTL代码“综合”为基于标准单元库的门级网表,并进行严格的功能与时序仿真验证。

- 物理设计:这是将逻辑网表转化为物理几何图形的核心阶段,包括布局(将单元放置在芯片上)、布线(连接所有单元)、时钟树综合、功耗分析以及设计规则检查等。物理设计的优劣直接决定了芯片的最终性能、功耗和良率。

- 签核与流片:在交付给晶圆厂制造前,进行最终的静态时序分析、电源完整性、信号完整性等签核验证。通过后,生成用于光刻的GDSII版图文件,交付制造,即“流片”。

二、VLSI设计面临的严峻挑战

随着工艺节点不断迈向7纳米、5纳米乃至更先进的制程,VLSI设计正面临一系列前所未有的“物理墙”和“经济墙”挑战:

- 功耗与散热瓶颈:晶体管密度激增导致单位面积功耗密度急剧上升,“功耗墙”已成为提升算力的首要限制。动态功耗、静态漏电功耗的管理,以及随之而来的散热问题,变得异常棘手。

- 设计复杂性爆炸:数十亿晶体管的设计规模使得验证工作量和复杂度呈指数级增长。确保功能正确性、避免设计缺陷的成本和时间占比越来越高。

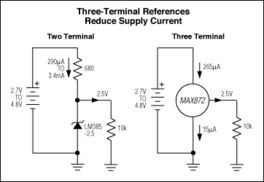

- 物理效应凸显:在纳米尺度下,互连线延迟已超过门延迟成为主导;量子隧穿效应、工艺波动、电迁移、串扰噪声等物理效应变得不可忽视,设计必须从“确定性”思维转向“统计性”和“可靠性”思维。

- 高昂的设计与制造成本:先进工艺节点的流片费用动辄数千万甚至上亿美元,且EDA工具、IP核授权费用不菲,使得VLSI设计成为资本和技术双密集的领域,提高了行业门槛。

三、技术演进与未来趋势

为应对挑战,VLSI设计方法学和支撑技术也在持续演进:

- 设计方法学革新:高层次综合、基于平台的IP复用、片上网络、异构集成(如Chiplet/小芯片技术)等,旨在提升设计抽象层次、复用率和系统集成效率。Chiplet技术通过将大芯片分解为多个小芯片并先进封装集成,成为延续摩尔定律、优化成本与性能的关键路径。

- EDA工具的智能化:人工智能与机器学习正深度融入EDA工具链,用于优化布局布线、加速设计空间探索、预测功耗和时序,甚至自动生成电路,显著提升设计效率和质量。

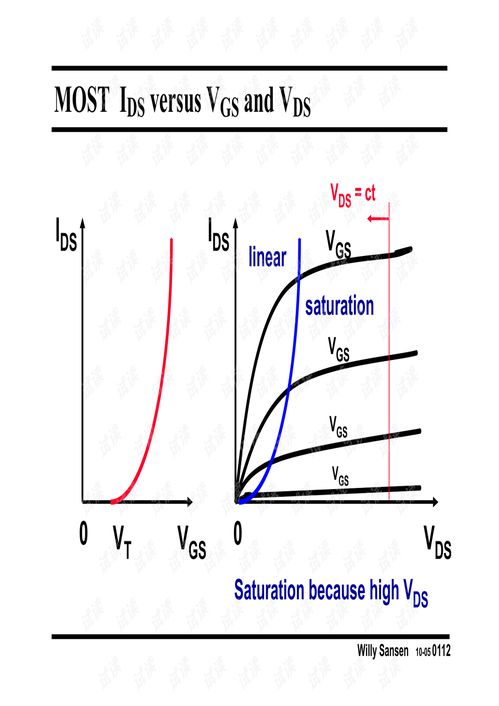

- 新器件与新架构探索:超越传统CMOS的器件(如CFET、二维材料晶体管)和革命性计算架构(如存算一体、 neuromorphic computing)的研究,旨在从根本上突破冯·诺依曼架构的瓶颈,为VLSI设计开辟全新赛道。

- 系统与封装协同设计:随着先进封装(如2.5D/3D IC)的成熟,设计范畴从单一的裸片扩展到整个封装系统,要求进行芯片-封装-电路板协同设计与优化。

****

超大规模集成电路设计是人类精密制造与智慧创造的巅峰体现之一。它不仅是将海量晶体管物理集成的技术,更是将复杂系统思想、算法需求与物理现实融合的艺术。面对后摩尔时代的挑战,VLSI设计正在从追求单一维度的微缩,转向面向应用、注重能效、融合软硬件的系统级协同创新。它将继续作为数字时代的基石,支撑起未来智能社会无处不在的计算需求。