随着电子技术的飞速发展,集成电路(IC)已成为现代信息社会的基石。其中,CMOS(互补金属氧化物半导体)技术以其低功耗、高集成度及良好的工艺兼容性,在模拟集成电路设计中占据主导地位。对于硬件工程师、学生及研究人员而言,掌握CMOS模拟集成电路设计的核心理论与开发实践至关重要。本文将以王永生教授的相关著作为引,结合硬件开发文档类资源(如CSDN等平台的下载资料),系统探讨集成电路设计的学习路径与资源应用。

一、CMOS模拟集成电路设计的基础理论

王永生教授在该领域的著作常被视为经典教材,深入浅出地讲解了MOS器件物理、单级放大器、差分放大器、电流镜、频率响应、噪声分析、反馈理论及运算放大器设计等核心内容。这些理论是理解模拟电路行为的根基,例如:

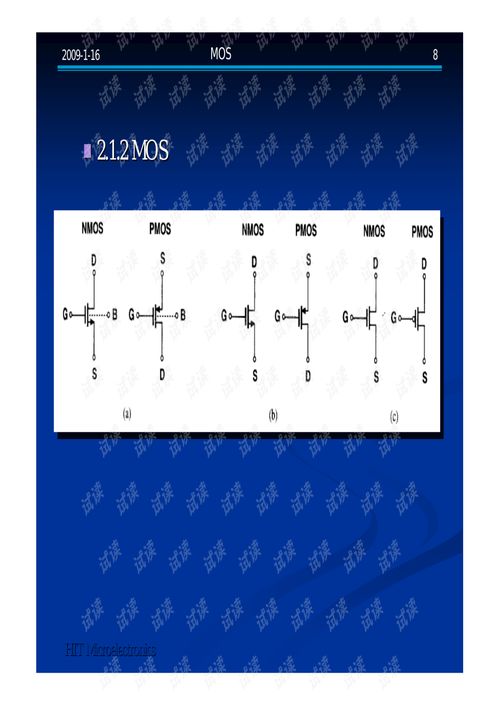

- MOS晶体管特性:理解阈值电压、跨导、输出电阻等参数,是设计放大器和电流源的基础。

- 反馈系统稳定性:通过波特图与相位裕度分析,确保电路在实际工作中的可靠性。

- 噪声与失真优化:在低功耗设计中,如何平衡性能与功耗是模拟设计的艺术。

理论学习不应停留在书本上,而需结合仿真工具(如Cadence、LTspice)进行验证。初学者可先从简单电路(如共源放大器)入手,逐步搭建复杂模块。

二、硬件开发文档类资源的应用

在实践环节,硬件开发文档类资源(如CSDN、GitHub、IEEE Xplore等平台的技术文章、项目源码及数据手册)能有效弥补理论与实践的鸿沟。以CSDN为例,其下载资源常包含:

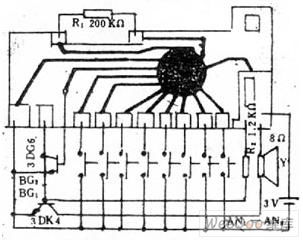

- 项目工程文件:提供完整的电路图、版图及仿真设置,帮助用户快速上手。

- 设计笔记与故障排查指南:资深工程师的经验,可避免常见设计陷阱。

- 工艺库文件:针对特定制造工艺(如TSMC 0.18μm),是进行实际流片前不可或缺的参考。

使用这些资源时,需注意甄别质量与时效性。建议优先选择高评分、有详细说明的文档,并关注行业最新动态(如FinFET工艺对模拟设计的影响)。

三、集成电路设计的全流程实践

一个完整的IC设计流程包括:

- 规格定义:明确电路性能指标(如增益、带宽、功耗)。

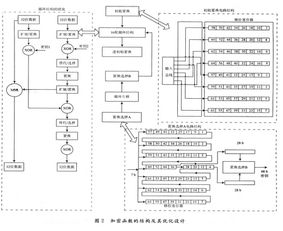

- 电路设计与仿真:使用工具进行原理图绘制和AC/DC/瞬态分析。

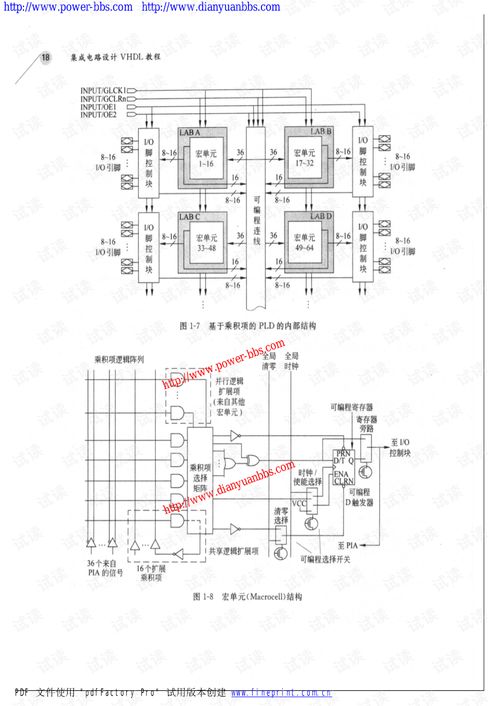

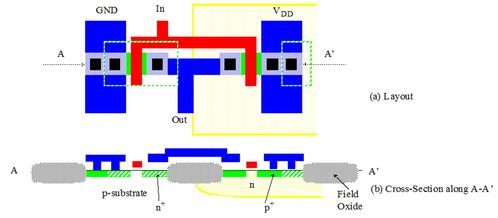

- 版图设计:考虑匹配性、寄生效应及设计规则(DRC),是连接设计与制造的桥梁。

- 后仿真与验证:提取版图寄生参数,确保电路在工艺角(Corner)下的稳定性。

- 流片与测试:实际制造并测量芯片性能,形成设计闭环。

资源平台上的案例(如ADC、PLL设计项目)可为各阶段提供参考。例如,通过分析一个开源运算放大器版图,能直观理解匹配布局的技巧。

四、学习建议与未来展望

对于初学者,建议:

- 理论结合实践:以王永生教材为主线,辅以在线课程(如Coursera的“CMOS Analog IC Design”)和仿真练习。

- 参与开源项目:在GitHub等平台贡献代码或复现经典电路,积累工程经验。

- 关注行业趋势:随着AIoT和汽车电子兴起,低功耗、高精度模拟电路需求日益增长,学习方向可向传感器接口、电源管理等领域拓展。

CMOS模拟集成电路设计是一门深度融合理论与技术的学科。通过系统学习经典著作(如王永生教授的作品),并高效利用CSDN等平台的硬件开发资源,设计者能够逐步构建从概念到芯片的完整能力。在半导体国产化的浪潮下,扎实的设计功底与持续的资源整合,将成为推动技术创新的关键力量。